450 ₽($)

в наличии на складе в Москве

Код товара: nortel024

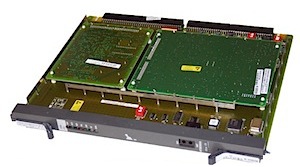

ставится на плату NTBK50A NTCK43 дочерняя плата D-канала PRI 2MB (EUROISDN/QSIG/MCDN)

D-Channel Daughterboard

The NTBK51 daughterboard provides two Multipurpose Serial Data Link (MSDL) based Downloadable D-channel (DCH) interfaces.

|

Example:

NTBK50AA 2Mb PRI, with

NTBK51AA D-Channel daughter Board, and

NTAK20BD Clock controller daughter Board

|

When the Dual D-Channel daughter Board is used with a NT5D97 Dual-port DTI2/PRI2 card (large system), the PRI cards DIP switches must set the MSDL device address. When used with a NTBK50 2.0 Mb PRI card (small system), only port 0 is used. Refer to the Circuit Card Reference NTP for details.

NTBK51 Programming:

LD 17, CHG ADAN:

ADAN DCH x

CTYP MSDL

DNUM xx

(Use the DNUM that was set by the DIP switches)

PORT 0

(0 for EVEN PRI loop, or small system / 1 for ODD PRI loop)

DES PRIISDN

USR PRI

DCHL XX

(associated Loop number)

OTBF 32

PARM RS422 DTE

DRAT 64KC

CLOK EXT

IFC D100

SIDE USR

CNEG 1

RLS ID 25

RCAP

MBGA NO

OVLR NO

OVLS NO

T200 3

T203 10

N200 3

N201 260

K 7

MSDL/DCH Maintenance:

Useful LD 96 MSDL/DCH maintenance commands. x is the MSDL device number (DNUM in LD 17), or DCH number.

When you enable an MSDL/DCH for the first time, or after a configuration change, always FDL it, and watch for the dots.

| ENL MSDL x (FDL, ALL) |

Enable MSDL device |

| DIS MSDL x (ALL) |

Disable MSDL device |

| RST MSDL x |

Reset MSDL device |

| STAT MSDL (x) (FULL) |

Get MSDL status |

| SLFT MSDL x |

Execute a self-test on MSDL device x |

|

| ENL DCH x (FDL) |

Enable DCH x and attempt to establish the link, and force download to MSDL |

| DIS DCH x |

Disable DCH x |

| RST DCH x |

Reset D-channel x, inhibit signaling |

| STAT DCH (x) |

Get status of one or all D-channels |

|

| ENL AUTO x |

Enable automatic recovery for DCH x |

| DIS AUTO x |

Disable automatic recovery for DCH x |

Daughter Board NTBK51AA

NTBK50AA 2Mb PRI, withNTBK51AA D channel daughter Board, andNTAK20BD clock controller daughter Board Meridian Option 51C-81C D-Channel

Daughter Board (NTBK51AA)

Meridian D CHANNEL DCHI DAUGHTER BOARD FOR THE OPTION 51C-81C MERIDIAN (NT5D12) Dual PRI Card.

The following applies to EUROPEAN EURO-ISDN PRI's.

Notes:

- Package 261 (EURO) must be present. LD 22: REQ prt, TYPE pkg

- If the PRI card is not a UDT), a D-Channel Daughterboard (e.g. NTBK51AA) is required on each PRI card.

- IF there's no existing PRI, LD 15: ISDN YES / PNI 1 in NET_DATA (must match PNI in the RDB) is required for the customer.

- There must be a Clock Controller Daughterboard (e.g. NTAK20BD) on at least one PRI per shelf for clocking purposes.

- LDN0 must be defined (LD 15, LDN_DATA) for ISDN PRI DID service. The length of LDN0 determines the number of trailing digits translated as the dialed DN on PRI DID routes - usually 4.

- AA PRI needs at least one trunk (channel) to be built before it will establish and STAT idle.

|

|

NTBK43AB 2Mb PRI, with a

NTBK51AA Daughter Board |

NTBK50AA 2Mb PRI, with a

NTBK51AA Daughter Board |

1. LD 17 (Define the Loop)

| REQ |

CHG |

| TYPE |

CEQU |

| PRI2 |

(Select an available loop number) |

| MGC |

(enter Loop Shelf Card, LSC, number of the Media Gateway PRI Card location) |

2. LD 17 (Build D Channel, must match parameters in the route)

| CHG |

CDB |

|

| TYPE |

ADAN |

|

| ADAN |

NEW DCH # |

Available D Channel Number |

| CTYP |

MSDL |

|

| MGC |

# # # |

Loop Shelf Card location of the D Channel Daughterboard on the PRI Card |

| PORT |

1 |

|

| USR |

PRI2 |

|

| DCHL |

## |

D Channel Loop number defined in the CEQU for the associated PRI Card |

| IFC |

EURO |

Normally EURO in Europe, but again it depends of the CO Switch interface and must match Route interface type |

| CNTY |

ETSI |

Normally this, but again, it depends on the CO Switch interface and must match Rout interface type |

| PINX_CUST |

0 |

|

| SIDE |

USR |

Slave to the controller. The CO is the controlling switch (NET) |

| OVLR |

YES |

Overlap Receiving Allowed. |

| DIDD |

|

Number leading of digits to be ignored for DID call during Overlap Receiving.

LD 96 ENL MON ALL followed by ENL MSGO (loop) and then ENL MSGI (loop) to observe the number of digits across the D Channel and count the number of digits to strip off to have only four digits showing for the PBX |

| OVLS |

YES |

Overlap Sending Allowed. |

3. LD 16 (Define Route Data Block)

| REQ |

NEW |

|

| TYPE |

RDB |

|

| CUST |

0 |

|

| ROUT |

## |

New Route Number |

| TKTP |

DID |

|

| DTRK |

YES |

|

| DGTP |

PRI2 |

|

| ISDN |

YES |

|

| MODE |

PRA |

ISDN Trunk Route (ISDN=yes) |

| IFC |

EURO |

This the norm, but it depends on the protocol of the CO Switch interface |

| CNTY |

ETSI |

This the norm, but it depends on the protocol of the CO Switch interface |

| DSEL |

VOD |

|

| AUTO |

NO |

Unless the trunks are to auto terminate to an Auto Attendant or attendant |

| ICOG |

IAO |

In And Out call processing |

| SRCH |

RRB |

Round Robin or random selection of trunks |

| ACOD |

## |

Access Code for the Route Dial Tone |

| TARG |

1-9 |

leave out the level of the TGAR of the instrument to allow ACOD dialing to access the route |

| CDR |

YES |

yes for CDR tracking until YES is no longer accepted consecutively |

| INC |

YES |

|

| LAST |

YES |

|

| QREC |

YES |

|

| OAL |

YES |

|

| AIA |

YES |

|

| OAN |

YES |

|

| OPD |

YES |

|

| NDP |

EXC 0 |

|

| MUS |

YES |

Yes if Music Route is available |

| MRT |

34 |

Music Route Number |

4. LD 14 (Define the Trunks)

| REQ |

NEW 30 |

We can build all 30 at once |

| TYPE |

DID |

|

| TN |

## ## |

Loop and Channel |

| CUST |

0 |

Customer Number |

| TRK |

PRI2 |

|

| PCML |

A |

Note: A= overseas/MU= eg: 61C to 61C |

| NCOS |

0 |

|

| ROUT |

# 1 |

Route and first member |

| CLS |

DTN |

Don't forget tone dialing |

5. LD 73 (System Timers and Loop Timers)

| CHG |

PRI2 |

|

| TYPE |

LPTI |

|

| LOOP |

|

Loop number of PRI card location or CEQU PRI2 defined loop |

| MFF |

AFF |

Normal, but if PRI Card is green with no activity, change to CRC or ask CO if CRC is being used |

| CHG |

PRI2 |

|

| FEAT |

SYTI |

System Timers |

| MGCLK |

|

Loop, Shelf, Card location of Clock Controller DB. Must be defined for each Clock Controller in shelf |

6. LD 96 (MSDL and D Channel activation)

| ENL MSDL # # # FDL |

Enable MSDL Loop Shelf Card) Force Down Load |

| STAT MSDL # # # |

Status of MSDL Loop Shelf Card |

| ENL DCH # |

Enables D Channel for PRI Card associated with active MSDL Card |

7. LD 60 (Enable PRI Loop)

| ENLL # |

Enables the Loop of the PRI/DTI Card |

| ENL CC # # |

Enables Clock Controller in Loop, Shelf of MGC |

| STAT # |

Status of PRI/DTI loop, channels should be IDLE |

Line Interface Pinout

The circuit is presented on pairs 23/48 (TX) and 24/49 (RX) of the card slots Amphenol (RJ-21).

A DSU/CSU cable (eg, NTBK04) is constructed as follows, although it may be necessary to cross TX and RX pairs:

| MDF | RJ48C | DB-15 | Signal | Description |

|---|

| 23 |

4 |

9 |

R |

Transmit ring to network |

| 48 |

5 |

1 |

T |

Transmit tip to network |

| 25 |

n/c |

2 |

FGND |

Frame ground |

| 24 |

1 |

11 |

R1 |

Receive ring from network |

| 49 |

2 |

3 |

T1 |

Receive tip from network |

* DSU/CSU = Data Service Unit/Channel Service Unit, eg, the PTT modem.

Loopback Adaptor Pinouts

| Loop pairs 23 to 24on the MDF, and the circuit should enable and go green.

DB15F - Short pin 1 to pin 3 and pin 9 to pin 11

RJ48C, 8-conductor Modular - Short pin 1 to pin 4 and pin 2 to pin 5

Note: An RJ-45 connector will fit an RJ-48 jack, but the key on an

RJ-48 connector will prevent it from plugging into an RJ-45 jack.

The D channel will not establish on a loop test.

|

|

Diagnosticsh3>

| TO DISABLE LOOP: |

LD 96

DIS DCH #

LD 60

DISL # |

| TO RE-ENABLE LOOP: |

LD 96

ENL DCH #

LD 60

ENLL # |

| TO REMOVE PRI CARD:

If the PRI card is removed

without following these steps,

it will cause the PBX to INI

|

DISABLE:

LD 96

DIS MSDL # # #

DIS DCH # (to make sure D Channel is disabled)

LD 60

DISL # (PRI card is safe to remove)

RE-ENABLE: (card re-inserted)

LD 96

ENL MSDL # # # FDL

ENENL DCH #

LD 60

ENLL # |

+новая NTAK20 Плата клок-контролера, ставится на плату NTBK50 Stratum 4 Clock Controller DaughterBoard Option 11

Задать вопрос о товаре  - отвечаем в течении нескольких часов.

- отвечаем в течении нескольких часов.